U 84 C 30 DC Schaltkreis für Zähler- und Zeitgeberfunktion \* In Entwicklung \*

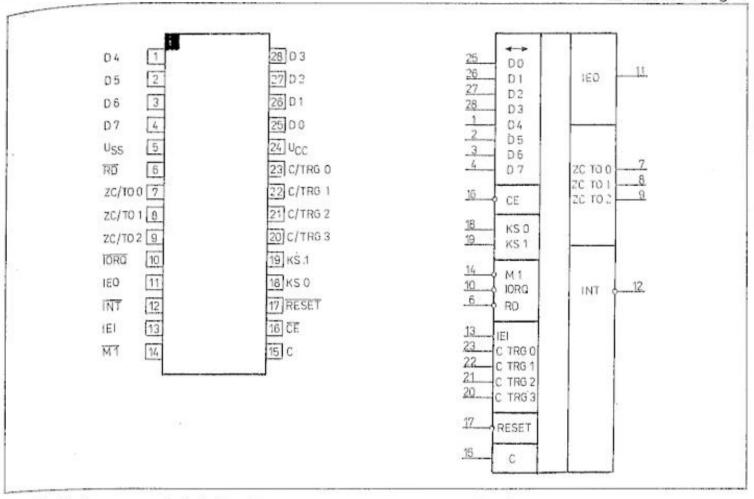

Anschlußbelegung und Schaltzeichen

Bauform: DIP-28, Plast (Bild 12)

Typstandard: TGL 42234

Kanalauswahl, Eingabe einer 2 Bit Adresse des vom

Mikroprozessor angesprochenen Kanals

### Bezeichnung der Anschlüsse

KS0, KS1

| IORQ                     | Ein-/Ausgabeanforderung, Eingang                   |  |

|--------------------------|----------------------------------------------------|--|

| IEI                      | Interruptfreigabe, Eingang                         |  |

| IEO                      | Interruptfreigabe, Ausgang                         |  |

| ĪNT                      | Interruptanforderung, Ausgang                      |  |

| $\overline{\mathrm{RD}}$ | CPU-Leseanforderung, Eingang                       |  |

| M1                       | CPU-Maschinenzyklus, Eingang                       |  |

| C                        | Systemtakt, Eingang                                |  |

| RESET                    | Rücksetzeingang                                    |  |

| C/TRG0 bis C/TRG3        | Takt- bzw. Triggereingang für den jeweiligen Kanal |  |

| D0 bis D7                | 8 Bit Datenbus, Ein-/Ausgänge, Tristate            |  |

| ZC/TO0 bis ZC/TO2        | Nulldurchgang des Rückwärtszählers bzw. Zeitgeber- |  |

|                          | meldung                                            |  |

|                          |                                                    |  |

Der CTC ist ein in CMOS-Technologie hergestellter programmierbarer Zähler-/Zeitgeberbäustein, der über vier voneinander unabhängige, softwareprogrammierbare Zähler-/Zeitgeberkanäle verfügt.

#### Folgende Varianten werden vom MME gefertigt

| Тур               | Taktfrequenz | Stromaufnahme<br>(typisch) | Schlafzustand |

|-------------------|--------------|----------------------------|---------------|

| U 84 C 30 DC 02   | 2,5 MHz      | 3 mA                       | möglich       |

| U 84 C 30 DC 04   | 4,0 MHz      | 3 mA                       | möglich       |

| U 84 C 30 DC 02-1 | 2,5 MHz      | 3 mA                       | nicht möglich |

#### Eigenschaften

- Alle Ein- und Ausgänge sind voll TTL-kompatibel,

- es wird nur eine 5 V Versorgungsspannung benötigt,

- es existieren vier voneinander unabhängige, softwareprogrammierbare 8 Bit Zähler/16 Bit Zeitgeberkanäle, jeder dieser Kanäle kann wahlweise als Zähler oder Zeitgeber verwendet werden,

- in der Betriebsart Zeitgeber sind Vorteiler durch 16 oder 256 für jeden Zeitgeberkanal möglich,

- es können Interrupts bei Erreichen von programmäßig festgelegten Zähler- oder Zeitgeberwerten programmiert werden,

- automatische Interruptvektorbereitstellung und Prioritätskodierung ohne zusätzlichen

Schaltungsaufwand durch Kaskadierung der Bausteine,

- die Ausgänge (ZC/TO0 bis ZC/TO2) der drei herausgeführten Kanäle sind zum direkten Anschluß von Darlington-Transistoren geeignet,

- die maximale Zählfrequenz in der Betriebsart Zähler ist  $f_C/2$ ,

- der CTC ist in einen Schlafzustand überführbar, bei dem die Stromaufnahme kleiner als  $10~\mu\text{A}$  wird.

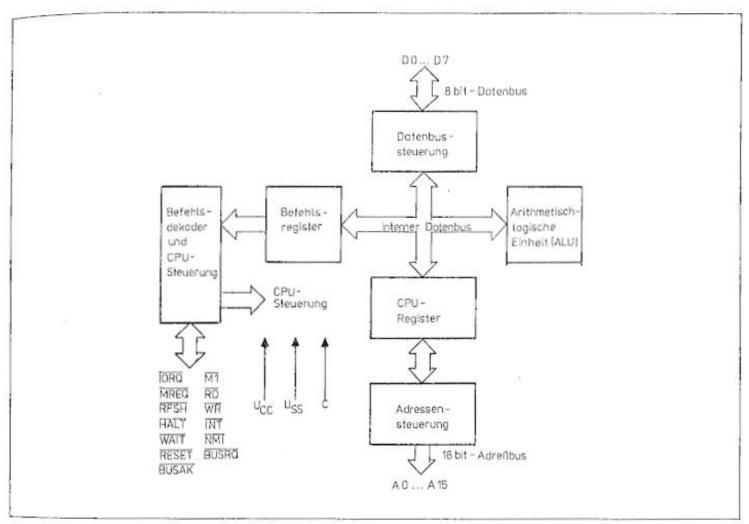

Der Zähler-/Zeitgeberbaustein enthält folgende Funktionseinheiten (siehe Übersichtsschaltplan):

Interface zur CPU

Der CTC kann direkt über die interne Bus-Interface-Logik an die CPU angeschlossen werden.

Interne Steuerlogik

Über eine interne Steuerlogik wird der Daten- und Steuerbus mit den vier Zähler-/Zeitgeberkanälen des CTC synchronisiert.

# . Interrupt-Steuerlogik

Die Interrupt-Steuerlogik behandelt die CPU-Interruptstrukturen entsprechend der festgelegten Priorität. Diese Priorität ist abhängig von der Stellung des CTC in der Prioritätskette. Jedem der vier Kanäle wird ein Interruptvektor zugeordnet, wobei der Kanal 0 die höchste Priorität besitzt.

## \_ 4 Zähler-/Zeitgeberkanäle

Jede Kanaleinheit besteht aus einem Zeitkonstantenregister (8 Bit), einem Kanalsteuerregister (8 Bit), einem Rückwärtszähler (8 Bit), einem Vorteiler und einer eigenen Steuerlogik. Der Vorteiler (8 Bit) ist auf die Werte 16 oder 256 programmiert.

Übersichtsschaltplan des CTC