# ZEISS

### **Schaltkreis**

U 1159 DC

1/89 (14)

vorläufige technische Daten

## Hersteller: VEB Forschungszentrum Mikroelektronik Dresden Betrieb des Kombinates VEB Carl Zeiss JENA

Programmierbarer HF-Teiler mit Vorverstärker

- Spezieller Schaltkreis für Frequenzmeß- und digitale Abstimm-Anzeige-Systeme (in Rundfunk- und Fernsehgeräten)

- 9 Teilverhälnisse programmierbar

- eine Versorgungsspannung 5 V ± 5 %

- Bingangsfrequenzbereich 600 kHz ... 125 MHz

- CMOS-Technologie (Standby-Betrieb möglich)

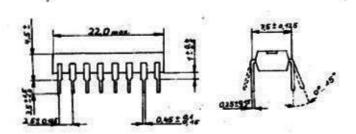

- Gehäuse: Bauform A1GH nach TGL 26713/02

Bild 1: Gehäuse

Der Schaltkreis U 1159 DC ist ein programmierbarer HF-Teiler mit Vorverstärker. Er ist für Eingangsfrequenzen von 600 kHz ... 125 MHz geeignet. Er besitzt folgende wählbare Teilverhältnisse:

10:1/32:1/33:1/64:1/65:1/100:1/101:1/110:1/111:1. Es stehen komplementäre Ausgangssignale zur Verfügung. Die Open-drain-Ausgänge sind abschaltbar. Ein "Standby"-Betrieb ist möglich. Der U 1159 DC eignet sich, bedingt durch das Angebot der dekadischen Teilverhältnisse

10:1 und 100:1, vorzüglich zur direkten Frequenzmessung. Durch die unmittelbar benachbarten Teilverhältnisse n:1 und (n+1):1 eignet er sich auch als Vorteiler für PLL-Synthesizer zur Abstimmung von HF-Empfängern (FM- und AM-Empfang). In Verbindung mit dem PLL-Synthesizer-Schaltkreis U 1056 DD ist durch Nutzung des in letzterem enthaltenen 5 Bit-Swallow-Zählers sowie des programmierbaren 10 Bit-Teilers, bei einem im U 1159 DC programmierten Teilverhältnisses 32/33:1 jedes ganzzahlige Teilverhältnis N im Bereich N = 1024 ... 32767 einstellbar.

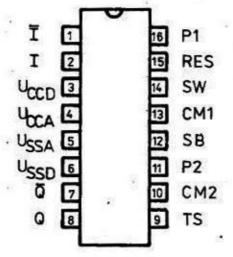

#### Anschlußbelegung

| Anschluß |                             | Bezeichnung                  |

|----------|-----------------------------|------------------------------|

| 1        | Ī                           | Signaleingang , invertierend |

| 2        | I                           | Signaleingang .              |

| 3        | UCCD                        | digitale Betriebsspannung    |

| 4.       | UCCA                        | analoge Betriebsspannung     |

| 5 .      | USSA                        | analoge Masse                |

| 6        | USSD                        | digitale Masse               |

| 7        | $\overline{\mathbf{Q}}_{i}$ | Invertierter Ausgang         |

| 8        | Q                           | Nichtinvertierter Ausgang    |

| 9        | TS                          | - "Tristate"-Eingang         |

| 10       | CM2                         | Teilmodus-Eingang 2          |

| 11       | P2                          | Programmiereingang 2         |

| 12       | SB                          | "Standby"-Eingang            |

| 13       | CM1                         | Teilmodus-Eingang 1          |

| 14       | SW                          | Aktivierungseingang          |

| 15       | RES                         | Rücksetzeingang              |

| 16       | P1                          | Programmiereingang 1         |

Bild 3: Anschlußbelegung

#### Funktionsbeschreibung

Der U 1159 DC besteht aus Vorverstärker sowie einer mehrstufigen Teilerlogik und ist als HF-Teiler für Frequenz-Meß- und -Synthesizer-Systeme konzipiert.

Der interne Vorverstärker des U 1159 DC sorgt für eine hohe Eingangsempfindlichkeit und ermöglicht somit eine passive Auskopplung der Oszillatorsignale. Dies gestattet das richtige Abschließen der Zuführungsleitungen und das Arbeiten mit geringen Signalamplituden. Der symmetrische Aufbau der Differenzeingangsstufe gestattet den Anschluß symmetrischer Leitungen. Der U 1159 DC besitzt 2 komplementäre Ausgänge (Q und  $\overline{Q}$ ), so daß das Ausgangssignal den Folgestufen mit beiden Polaritäten angeboten wird. Somit können sowohl Schaltungen angesteuert werden, die auf die positive, als auch solche, die auf die negative Flanke aktiv reagieren. Durch die Ausführung der Ausgänge als Opendrain-Stufen ist die Ansteuerung mit TTL- oder CMOS-Logikpegeln gewährleistet.

Über den Rücksetzeingang "RES" (high-aktiv) können die Ausgänge Q und  $\overline{Q}$  definierte Logikpegel erhalten; RES = H hat Q = L und  $\overline{Q}$  = H zur Folge. Liegt RES statisch auf H-Pegel, werden die Ausgänge festgeklemmt, so daß keine Frequenzteilung stattfindet.

Die Programmiereingänge P1 und P2 dienen zur statischen Einstellung der Hauptteilverhältnisse (10, 32, 64 und 100), während die Teilmoduseingänge CM1 und CM2 als Steuereingänge zur dynamischen Veränderung der Hauptteilverhältnisse, z. B. 32:1 in 33:1, 64:1 in 65:1 bzw. 100:1 in 101:1, verwendet werden können.

Wird der Aktivierungseingang SW = L gesetzt, werden die Signaleingänge aktiviert.

| Teil | Lve | er | näl | tnis | P1  | P2  | CM1 | CM2 |      |

|------|-----|----|-----|------|-----|-----|-----|-----|------|

| 10   | :   | 1  |     | *    | н   | н   | н   |     |      |

| 32   | :   | 1  |     | 20   | L   | L   | P   |     |      |

| 33   | :   | 1  | ٠   |      | L   | L   | H   | •   |      |

| 64   | :   | 1  |     |      | н   | · L | L   |     |      |

| 65   | :   | 1  |     |      | H   | L   | H   | •   |      |

| 100  | :   | 1  |     |      | F   | H   | H   | , H |      |

| 101  | :   | 1  |     |      | L   | н   | r.  | H   |      |

| 110  | :   | 1  |     | - C  | L   | н   | H   | L   | 0.50 |

| 111  | :   | 1  |     |      | L - | H   | L   | L   |      |

Anmerkung: # bedeutet beliebiges Steuersignal

Das Teilverhältnis 10 : 1 wird nur quasistatisch (bei 10 MHz) gemessen. Über den Eingang "TS" können, mit TS = L, die Ausgänge abgeschaltet (hochohmig) werden.

Mit einem weiteren Signal, zugeführt über den Standby-Eingang "SB", kann der U 1159 DC in den Schlafzustand gebracht werden. Hierzu ist SB = L erforderlich. Die Ausgänge werden nun hochohmig und die Stromaufnahme des Schaltkreises geht auf I<sub>CCSB</sub> zurück.

| 5 W.M                                | Kurzzeichen       | min.               | max.                 | Binheit           |

|--------------------------------------|-------------------|--------------------|----------------------|-------------------|

| Betriebsspannung                     | UCCA, UCCD        | -0,3               | 7,0                  | v                 |

| Spannung an allen<br>Eingängen       | v <sub>I</sub>    | -0,3               | ucc+0,3              | Υ                 |

| Spannung an Q, Q                     | <b>v</b> 0.       | -0,3               | 10                   | <b>v</b> ,        |

| Verlustleistung                      | P <sub>tot</sub>  | 20 E               | 0,25                 | w                 |

| Umgebungstemperatur                  | 297               | 0                  | 70                   | °C .              |

| Ausgangsdauerstrom                   | I <sub>Omax</sub> |                    | 20                   | mA .              |

| Betriebsbedingungen                  | (Alle Spannunger  | sind suf U         | SSD bzw. USSA        | (Masse) bezogen   |

|                                      | Kurzzeichen       | min.               | max.                 | Einheit           |

| Betriebsspannung                     | v <sub>cc</sub>   | 4,75               | 5,25                 | <b>V</b>          |

| Steuereingänge                       | · .               |                    | ψ                    |                   |

| L-Eingangsspannung                   | UIL               | -0,3               | 1                    | <b>y</b>          |

| H-Eingangsspannung<br>Signaleingänge | TH.               | U <sub>CC</sub> -1 | U <sub>CC</sub> +0,3 | <b>y</b>          |

| Eingangsfrequenz                     | f                 | 0,6                | 125                  | MHz               |

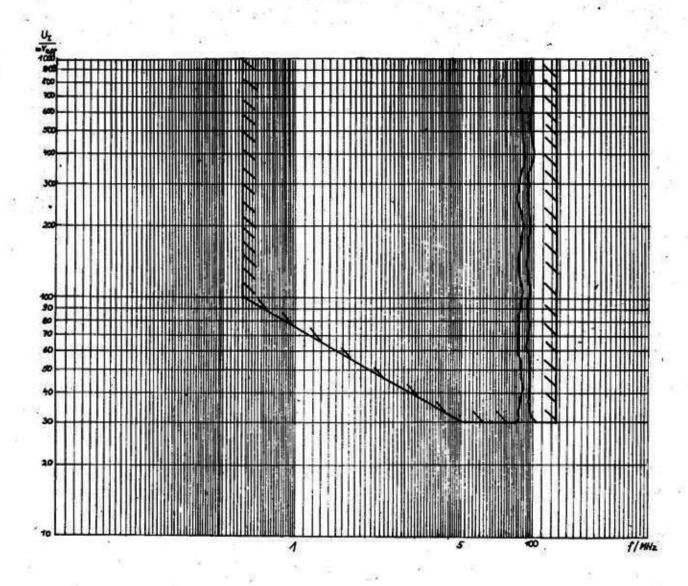

| Fingangsspannung<br>f = 0,6 MHz      | u <sub>I</sub>    | 1001)              | 1000                 | mV <sub>eff</sub> |

| f > 5 MHz                            | 6                 | 30                 | 1000                 | mV <sub>eff</sub> |

| Haltezeit                            | t <sub>H</sub>    | 0                  | -                    | ns                |

| Set-up-Zeit 1                        | t <sub>S1</sub>   | . 20               | ***                  | ns                |

| Set-up-Zeit 2                        | t <sub>S2</sub> . | 1/f [GHz]+2        | o <b>-</b>           | ns                |

<sup>1)&</sup>lt;sub>siehe Bild</sub> 3

#### Kennwerte

| •                    | Kurzzeichen       | min.             | max. | Binheit |

|----------------------|-------------------|------------------|------|---------|

| L-Ausgangsspannung   | U <sub>OL</sub>   |                  | 2,4  | A 5)    |

| H-Ausgangsspannung   | U <sub>OH</sub>   | 8,5              |      | v 2)    |

| Stromaufnahme        | ICC               | -1               | 40   | "mA "   |

| Standby-Stromaufnahm | e Iccsb           | E .              | 20   | /uA     |

| Eingengsleckstrom    | IIL               | -3               | 3    | , \my   |

| Ubergangszeit        | , tQTHL           | . <del>.</del> . | . 25 | ns .    |

| Q, Q                 | <sup>t</sup> QTLH | . •              | 50   | ns      |

|                      |                   |                  | 38   | 54      |

<sup>1)</sup> Zwischen I und T bei Generatorwiderstand von 75 Ohm

#### Applikative Hinweise

Beim Rücksetzen des Teilers ist zu beachten, daß mindestens 20 ns (Set-up-Zeit 1) vor der H/L-Flanke des RES-Signales und bis mindestens zu dieser Flanke (Haltezeit) die Signale an den Teilmoduseingängen CM1/CM2 gültig anliegen müssen, damit das durch CM1 und CM2 festgelegte Teilver hältnis in der ersten Ausgangsperiode realisiert wird.

Bei dynamischem Umschalten (d. h. während des Betriebes) der Teilverhälnisse ist die Set-up-Zeit 2 zu beachten (CM-Vorhalt). Die CM1/CM2-Signale müssen eine Zeit t<sub>S2</sub> + 20 ns vor der H/L-Flanke des Ausganges Q gültig anliegen. Die Einstellung der Teilverhälnisse für die Ausgangsperiode N erfolgt also in der Periode N-1.

Das Tastverhältnis der Ausgänge Q und Q hängt vom gewählten Teilverhältnis Y ab. Es gilt:

Bei geradem Teilverhältnis Y werden Y/2 Eingangstakte und bei ungeradem (Y-1)/2 + 1 Impulse benötigt ehe die Ausgänge erstmalig ihren Pegel ändern. Ausnahmen sind die Teilverhältnisse

110 : 1 und 111 : 1; bei erstgenanntem erfolgt die Reaktion nach 60 und bei letzterem nach 61 Takten.

Wird nur ein Signaleingang einer der Eingangsstufen benutzt, so ist der andere freie Eingang über einen Keramikkondensator von ca. 22 nF an Masse zu legen.

Wie bei allen CMOS-Schaltkreisen sind offene Steuereingänge zu vermeiden. Diese können entweder direkt oder über Widerstände an Betriebsspannung bzw. Masse gelegt werden.

Durch die hohen Eingangsfrequenzen bis zu 125 MHz sind für den Schaltungsentwurf die für die HFTechnik allgemeingeltenden Grundsätze zu beachten. Das sind z. B. Abblockung der Betriebsspannung,

kurze und impedanzarme Leitungen zu den Signaleingängen, sorgfältige Konstruktion der Leiterkarten.

Als Kondensatoren sind Keramikkondensatoren zu verwenden, die möglichst nahe an den entsprechenden

Anschlüssen des U 1159 DC anzubringen sind.

Für den Schaltkreis U 1159 DC gelten die Handhabungsvorschriften für elektrostatisch empfindliche Bauelemente.

<sup>2)</sup>Lastwiderstand von 470 Ohm gegen 9 V und 30 pF Kapazität gegen Masse.

Bild 3: Toleranzfeld der Eingangsspannung

Die vorliegenden Detenblätter dienen ausschließlich der Information! Es können daraus keine Liefermöglichkeiten oder Produktionsverbindlichkeiten abgeleitet werden. Änderungen im Sinne des technischen Fortschritts sind vorbehalten.

Herausgeber

veb applikationszentrum elektronik berlin im veb kombinet mikroelektronik

Mainzer Straße 25

Berlin, 1035

Telefon: 5 80 05 21, Telex: 011 2981 011 3055